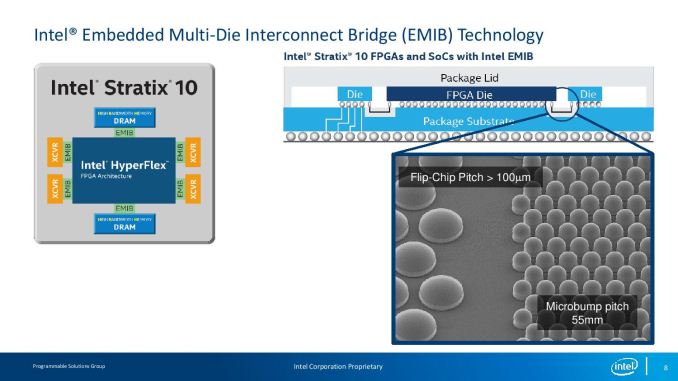

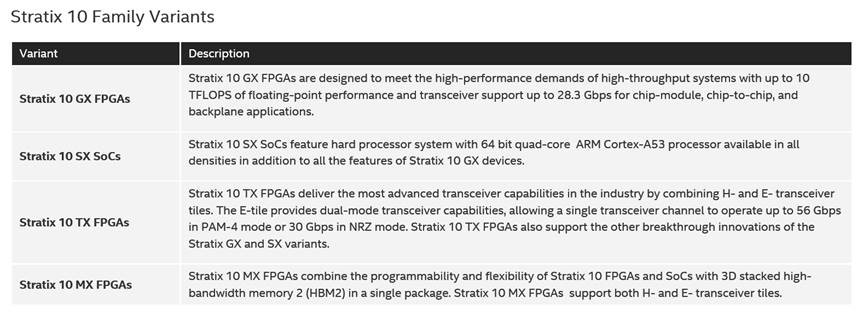

One of the key takeaways from Hot Chips last year was that Intel’s EMIB strategy was going to be fixed primarily in FPGAs to begin with. Intel instigated a bridge and chiplet strategy: with the right FPGA, up to six different chiplets can be added via EMIB in a single package. This is well beyond the single EMIB implementation coming to consumers. Intel has already been selling its Stratix 10 family of FPGAs that have additional functionality through EMIB for a number of months, however today Intel is announcing the latest member of that family, one that has the ability to include 58G transceivers: the Stratix 10 TX.

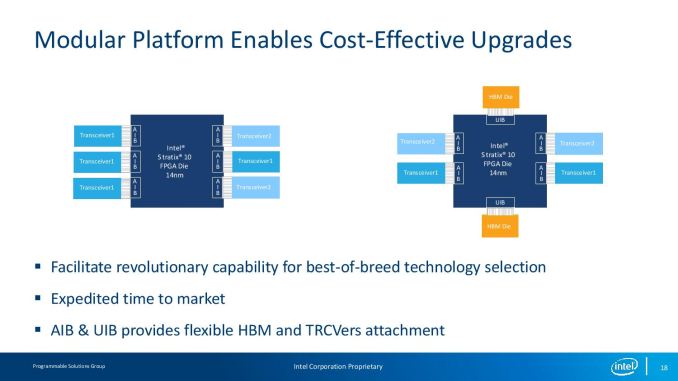

Intel will offer different variants of the Stratix 10 TX, from 600k logic elements with two chiplets up to 2.8 million logic elements with six chiplets. Five of the tiles are capable of taking the new 58G transceivers, enabling up to 144 transceivers in a single package. The sixth tile is used for PCIe. While the central FPGA is built on Intel’s 14nm process technology, the transceivers will be built upon TSMC’s 16FF process, due to Altera’s history of using TSMC for its analog hardware. Intel states that the transceivers in play can go down to 1 Gbps if needed, enabling backwards compatibility with existing networks. These transceivers were first demonstrated back in March 2016, finally making it to market.

Intel is calling the new transceivers dual-mode 58G, with 4-levels of pulse-amplitude modulation (PAM4) and 30 Gbps non-return-to-zero. Previously these were (and have been called) 56G, but Intel is using the term 58G because it believes that its solution will perform better than other 56G solutions on the market, enough to call it a 58G device.

The aim for these new Stratix 10 devices is for driving networking bandwidth needs for centralized base stations and network virtualization. The latter here is critical for 5G implementation, where compute happens in edge networks and VMs are transferred around to enable compute that has to happen closer to the device, especially with software defined networking. The Stratix 10 also features a range of IP cores, for 100GbE MAC and FEC, and the transceivers are built through a range of Intel and third-party IP.

We are told from Intel that using EMIB in conjunction with the new chiplets enables for a much lower power product than previous designs. Intel offers customers substantial training, but EMIB implementations are essentially transparent to the design: the upside being bandwidth related and the ability to create use cases from that functionality.

Alongside the Stratix 10 TX, Intel will also be offering a TX version with HBM2 (high-bandwidth memory). Within the largest design, the package can have two 4GB HBM tiles paired with three 58G transceivers and one 28G transceiver. That last one is 28G because it also has a hard PCIe connection. The HBM2 memory can run at either 800 MHz or 1 GHz depending on the product.

Intel is shipping the Stratix 10 TX family from today.

Related Reading

- Hot Chips: Intel EMIB and 14nm Stratix 10 FPGA Live Blog

- Intel to Acquire FPGA-Specialist Altera for $16.7 Billion

- Intel to Create new 8th Generation CPUs with AMD Radeon Graphics with HBM2 using EMIB

from AnandTech http://ift.tt/2CKBuKB

via IFTTT

0 comments:

Post a Comment