The market of automobiles is changing. Modern cars use more electronics than ever and adoption of electronic components in general and processors in particular is not going to slow down. All major automakers are working on self-driving vehicles, which means that cars of the future will need even more sophisticated SoCs.

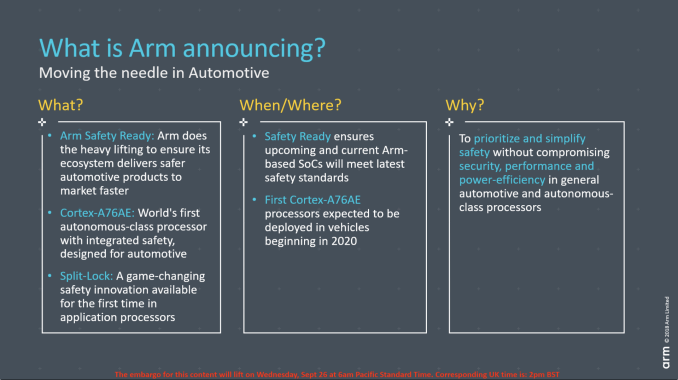

As demand for components needed for autonomous cars is about to explode in the coming years, it is not surprising that more companies start to develop solutions specifically designed for such vehicles. Arm on Wednesday launched its new Arm Safety Initiative that is aimed to develop solutions for self-driving cars. In addition, the company launched its Cortex-A76AE, its first processor IP designed specifically for autonomous vehicles.

Arm Safety Initiative

Arm is clearly not a newcomer to the automotive market. The company’s general-purpose and real-time cores have been used by makers of various vehicles since 1996. Nowadays Arm’s IP is used for ADAS (collision avoidance, cruise control, etc.), connectivity, infotainment, powertrain control, and other components of the cars.

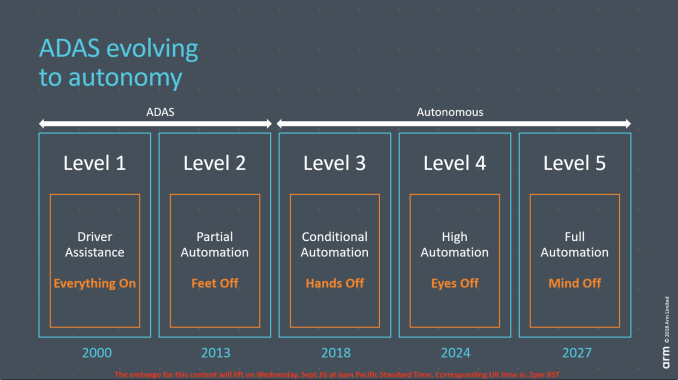

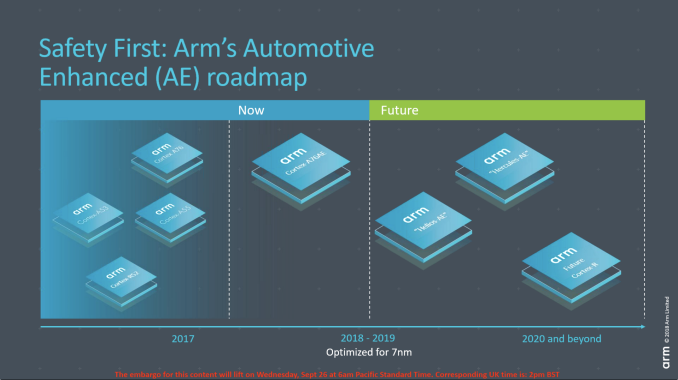

Meanwhile, up until lately Arm supplied automakers its IP originally developed for various devices in general. By contrast, the Arm Safety Initiative is a multi-year program under which the company will develop Automotive Enhanced (AE) custom and semi-custom solutions for autonomous cars. Initially, Arm will start with solutions for Level 3 self-driving vehicles, but over time it will offer products built for Level 4 and Level 5 autonomous cars sometimes in 2020 and beyond.

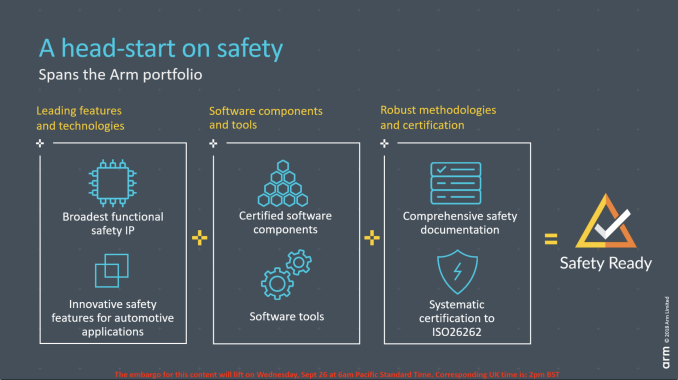

The Arm Safety Initiative spans the company’s entire portfolio of products and will include certified physical IP blocks to be made using specific process technologies, ISO 26262-certified software tools and components, safety documentation, and so on.

Right now, Arm only talks about its Cortex-A76AE processor for self-driving cars, but the grand plan includes Automotive Enhanced processors based on the Helios and the Hercules microarchitectures. Besides, Arm intends to offer AE versions of its future Cortex-R cores sometimes in 2020 and beyond. While Arm is developing AE flavors of its future IP, it will keep offering its existing cores (e.g., Cortex-A72, Cortex-R5, Cortex-R52, Cortex A53, Cortex-M4, Cortex-M7, Cortex-M44, etc.) to developers of SoCs for automotive market.

The implementation of the ASI program will enable makers of cars to obtain IP that will make their systems for autonomous driving significantly more energy efficient and cheaper, which will make self-driving vehicles more affordable in general. Besides making the said systems cheaper, Arm Safety Initiative also promises to speed up their development.

Arm’s Cortex-A76AE: The First Member of the AE Family

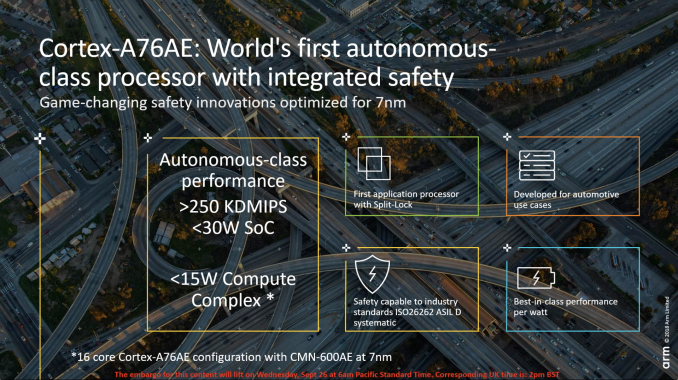

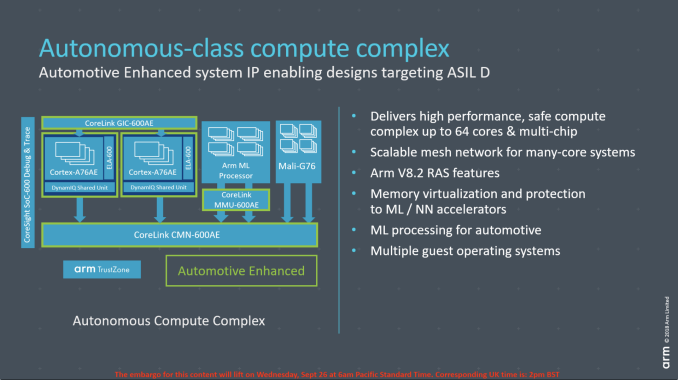

The first product that is a part of Arm’s Safety Initiative is the company’s Cortex-A76AE processor with integrated redundancy. As the model number suggests, a Cortex-A76AE compute complex relies on up to 16 Cortex-A76 cores that support all the RAS (reliability, availability, serviceability) capabilities featured by the Arm v8.2 microarchitecture, and work in work in Split-Lock mode to ensure reliability.

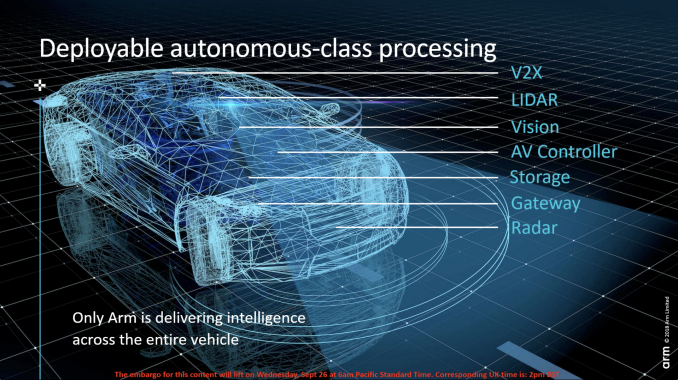

Actual SoCs based on the Cortex-A76AE can scale to up to 64 cores. Besides general-purpose compute cores, Arm’s autonomous-class compute complexes also integrate Mali-G76 graphics cores, ARM’s ML cores, and other necessary IP. Besides, the complexes are set to support Arm’s memory virtualization and protection technologies required for flawless operation of ML and NN accelerators.

According to Arm, a 30-Watt 16-core Cortex-A76AE SoC implementation made using TSMC’s 7nm process technology has performance of over 250 KDMIPS, which is enough for today’s applications. If a customer wants a higher performance, it may build into more cores, or even use more than one SoC.

Raw performance is what actually matters for self-driving vehicles. Modern Level 3 autonomous cars run multiple programs at once and that is not going to change anytime soon. According to Arm, software for a Level 5 self-driving auto will contain 1 billion lines of code. By contrast, software used to run a Boeing 787 Dreamliner contains 14 million lines of code.

Arm’s Split-Lock: Redundant Computing in Hardware

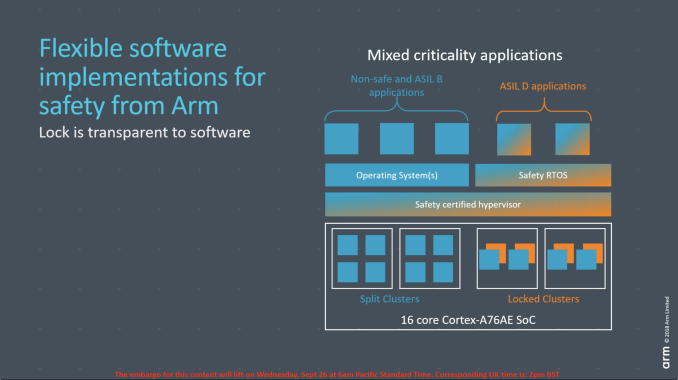

Now, time to talk about the key feature of Arm’s Cortex-A76AE — the Split-Lock technology. The Split-Lock feature enables SoC developers to use the cores in two modes: the Split Mode to runs the cores independently and achieves higher performance, and in the Lock Mode a core is run in lockstep with a paired core, running the same code and monitoring for any kind of divergences that would be then reported as an error, and failure recovery mechanisms would take over (or at least a driver will be notified).

The Lock Mode somehow resembles how HP’s NonStop works for mission-critical applications, but the key difference is that Arm’s solution relies completely on hardware and is therefore compatible with any software (think AutoWare, Deepscale, Linaro, Linux, QNX, etc.).

Arm proposes to use the locked clusters for ASIL-D application that are critically important for safety. By contrast split clusters are intended for ASIL-B apps like infotainment. Given the flexibility of Arm’s hardware-only approach, the Split-Lock can be used by any automaker to run almost any software while ensuring either performance and error-free computing.

Related Reading:

- Arm's Cortex-A76 CPU Unveiled: Taking Aim at the Top for 7nm

- Arm Unveils Client CPU Performance Roadmap Through 2020 - Taking Intel Head On

- Arm and Samsung Extend Artisan POP IP Collaboration to 7LPP and 5LPE Nodes

- Hot Chips 2018: Arm's Machine Learning Core Live Blog

from AnandTech https://ift.tt/2OgpVVi

via IFTTT

0 comments:

Post a Comment