Rambus has developed a comprehensive PCIe 5.0 and CXL interface solution for chips built using 7 nm process technologies. The interface is now available for licensing by SoC designers and will enable them to bring PCIe 5.0/CXL-supporting hardware to the market faster.

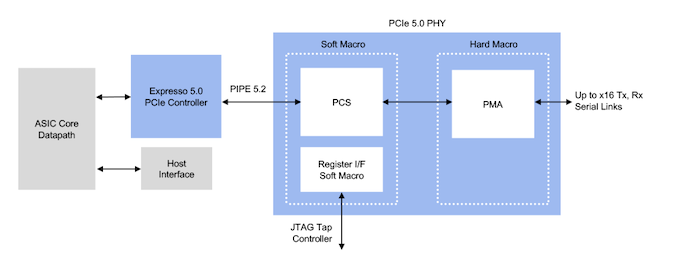

Rambus’ PCIe 5.0 solution includes a controller core originally developed by Northwest Logic (which was recently acquired by Rambus) and is backwards compatible with PCIe 2.0, PCIe 3.0 and PCIe 4.0, as well as a PHY that also supports CXL. The solution supports 32 GT/s per lane data transfer rate and is designed for advanced 7 nm FinFET process technologies. Besides the IP itself, Rambus will also offer design, integration, and support services to speed up the development process.

Rambus believes that its PCIe 5.0 solution will be used by developers of processors for AI, HPC, storage, and 400 GbE networking applications. Considering the fact that many of the upcoming accelerator chips will use the CXL interface, it is important that Rambus’ PHY also support the new technology.

Rambus did not disclose how much its PCIe 5.0 solution will cost to its licensees.

Related Reading:

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

- Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Source: Rambus

from AnandTech https://ift.tt/2Kk8eBf

via IFTTT

0 comments:

Post a Comment