The Gen-Z Consortium this week released Physical Layer Specification 1.1 for Gen-Z interconnects. The new standard adds enhanced support for PCIe Gen 5 as well as Gen-Z 50G Fabric and Local PHY. The publication of the new PHY revision enables chip developers to implement support for the technologies in upcoming devices featuring Gen-Z interconnects.

Designed to offer high bandwidth and low latency for connections between processors, co-processors/accelerators, and memory/fast storage, Gen-Z 1.0 uses a PCIe physical layer and a modified IEEE 802.3 Ethernet electrical layer standards to provide per-lane speeds of up to the 56 GigaTransfers/second. The Gen-Z 1.0 physical layer specification only defined usage of PCIe Gen 1-4 protocols as well as a 25 GT/s PHY. Thus, to take advantage of all the capabilities of the Gen-Z 1.0 core specification, one needs to comply with the Gen-Z PHY that describes logical, functional, electrical, and channel characteristics for various PHY layers.

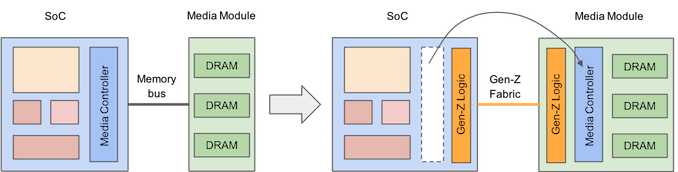

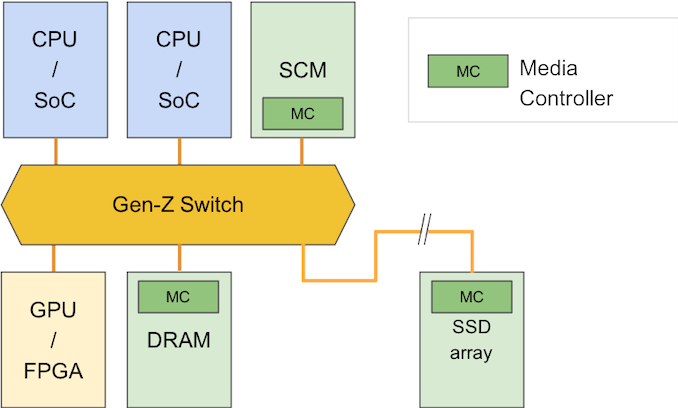

From CPU-memory interface to media-agnostic fabric

The Gen-Z Physical Layer Specification 1.1 defines how to implement a Gen-Z layer capable of operating at PCIe Gen 5 32 GT/s per lane speeds. Revision 1.1 also outlines how to implement a medium to reach a Gen-Z-E-PAM4-50G-Fabric link with a raw data rate of 53.125 GT/s per lane using a 4-level Pulse Amplitude Modulation (PAM4) signaling over the fabric with an ultra-low-latency Phit Forward Error Correction (Phit FEC) encoding using a BCH codeword. Finally, the specification 1.1 describes the implementation of a very short reach Gen-Z-E-PAM4-50G-Local link at 53.125 GT/s per lane using a PAM4 signaling with Forward Error Correction (raw data-rate of 47.222 GT/s).

System architecture with Gen-Z

In addition to the Physical Layer Specification 1.1, Gen-Z has eight more final specifications and five draft specifications available.

Related Reading

- Hot Chips 31 Live Blogs: Gen-Z Chipset for Exascale Fabric

- SMART Modular Shows Off 256 GB Gen-Z Memory Module

- Hot Chips 31 (2019) Programme Announced: Zen, Navi, POWER, Lakefield, Gen-Z, Turing, Lisa Su Keynote

- Gen-Z Interconnect Core Specification 1.0 Published

- Gen-Z Consortium Formed: Developing a New Memory Interconnect

Source: Gen-Z Consortium

Image Source: PLDA

from AnandTech https://ift.tt/2LJeOlE

via IFTTT

0 comments:

Post a Comment