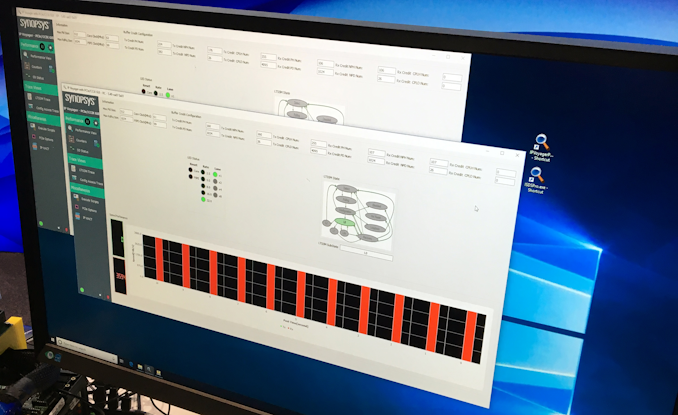

Synopsys, one of the leading developers of chip development tools and silicon IP, demonstrated its CXL over PCIe 5.0 as well as CCIX 1.1 over PCIe 5.0 solutions at ArmTechCon 2019. The showcase indicates that the company’s IP is up and running, and is ready to be licensed by interested parties.

CXL and CCIX are chip-to-chip interconnect protocols for connecting processors to various accelerators that maintains memory and cache coherency at low latencies. Both protocols are designed for heterogeneous systems that use traditional CPUs along with accelerators featuring scalar, vector, matrix, and spatial architectures. Both CXL 1.0/1.1 as well as CCIX 1.1 use PCIe Gen 5 PHY stack at 32 GT/s per lane and support different link width natively. Aiming the same market segment and using the same physical interface, the CXL and CCIX protocols have numerous differences both on hardware as well as firmware/software side of things and will therefore compete against each other. Meanwhile, providers of silicon IP are gearing up to support both CXL and CCIX as they have a broad range of customers.

Synopsys recently introduced its 16-lane DesignWare CXL IP solution for SoCs to be made using 16 nm, 10 nm, and 7 nm FinFET process technologies. The package comprises the company’s CXL 1.1-compliant controller (supporting CXL.io, CXL.cache, CXL.mem protocols), silicon-proven PCIe Gen 5 controller, silicon-proven 32 GT/s PHY (allowing >36 dB channel loss across power, voltage, and temperature variations for long reach connections), RAS capabilities, and VC Verification IP.

The company yet has to formally announce availability of its DesignWare CCIX 1.1 IP package that will enable implementation of a CCIX 1.1 over PCIe Gen 5 at 32 GT/s speed, but at ArmTechCon the company demonstrated that the solution is already functional.

Both showcases were carried out using an FPGA as well as special equipment, but not using actual chips, which is not particularly surprising. But even such demonstrations indicate that Synopsys is ready not only with competitive PCIe 5.0 PHY and IP, but also with CXL and CCIX implementations.

Related Reading:

- Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- USB 3.2 at 20 Gb/s Coming to High-End Desktops This Year

Sources: David Schor/Twitter, Anshel Sag/Twitter, Synopsys

Images by Ryan Smith/AnandTech

from AnandTech https://ift.tt/328zklF

via IFTTT

0 comments:

Post a Comment