Aside from specific events relating to Xilinx or Altera/Intel, we don’t cover much FPGA news. FPGAs by their very nature are very focused pieces of hardware, and it’s usually a binary option if you need one. They can be difficult to build for without the right expertise as well, but if you have the right engineer and the product needs one, then sometimes it’s a very easy sell. In recent months the key noise on FPGAs has been around SmartNICs, 5G network accelerators, and simulation – both Intel and Xilinx announcing new hardware this year relating to the latter. In order to support FPGA developers, AIC was showing off one of its new server builds at Supercomputing.

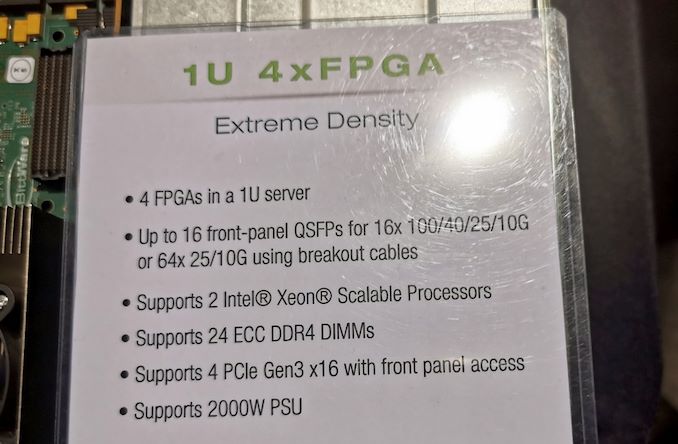

The key with FPGA simulation is often timing and/or accuracy, and accelerated networking is often latency and co-processor bound. All of these problems can be improved through the density of the hardware. AIC’s new 1U server piles on the extreme density, allowing for two Xeon Scalable CPUs and four 300W FPGAs in 1.75 inches. These are air cooled, and backed by redundant 2000W power supplies.

In the example box on display, AIC showed FPGAs with QSFP+ ports with slots requiring additional memory, making for a very packed server. Each of the PCIe cards with an FPGA are installed via the front panel, which will allow for adjusting the connectivity between servers a little easier. AIC stated that these servers are typically engineered for 5G. We were told that this is where a lot of business is right now, with R&D focused on making sure they have the right silicon design, accelerators, and co-processors in place.

AIC didn’t have a specific SKU name to give to this design just yet, as they are still going through testing and validation, but expect it to be ready for customers soon.

Related Reading

- AIC Shows Dual NF1 to U.2 SSD Adapter

- The Reality of SSD Capacity: No-One Wants Over 16TB Per Drive

- AIC’s Grays Peak Server with Intel ‘EDSFF’ Ruler SSDs

- Intel’s EMIB Now Between Two High TDP Die: The New Stratix 10 GX 10M FPGA

- Xilinx Announces World Largest FPGA: Virtex Ultrascale+ VU19P with 9m Cells

from AnandTech https://ift.tt/2Rnfi4k

via IFTTT

0 comments:

Post a Comment