The DisplayPort 2.1 specifications were officially released by VESA on Monday, and this was followed up by USB-IF's announcement of the release of the 80 Gbps USB4 v2 specifications yesterday. These have have brought to fore the significant engineering efforts put into creating a unified protocol capable of handling the external I/O bandwidth requirements of tomorrow's computing systems. Today, Intel is announcing the demonstration of early prototypes for next-generation Thunderbolt based on the USB4 v2 and DisplayPort 2.1 specifications.

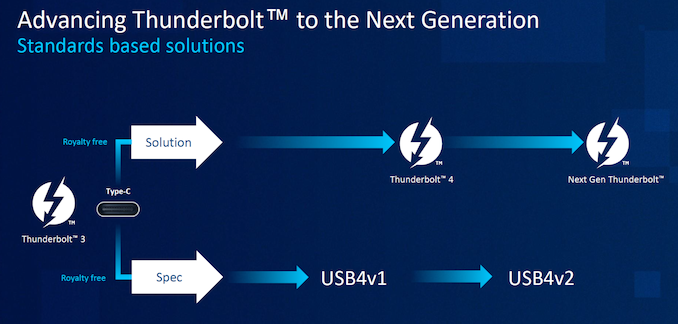

Intel's donation of the Thunderbolt 3 specifications to the USB promoters group to form the basis of USB4 has had its share of pros and cons. On one hand, the convergence of the Type-C connector ecosystem theoretically achieved the goal of minimizing end-user confusion, and the royalty-free spec for PCIe tunneling opened up the market to other silicon vendors like ASMedia. However, it also created consumer angst as most of the attractive features of USB4 (such as the 40Gbps bandwidth and compatibility with PCIe tunneling) were entirely optional features. That said, it did enable Intel to market Thunderbolt ports as the Type-C that could do it all. Intel's demonstration of Next Generation Thunderbolt also included a sneak peek into its specifications, even though certain aspects are yet to be finalized. Before delving deeper into Intel's press release, a quick recap of the 80 Gbps USB4 v2 specifications announcement is necessary.

USB4 v2 Updates

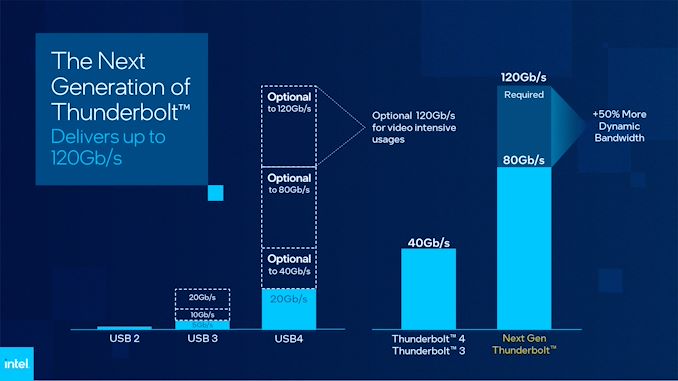

USB4 v2 builds upon the multi-protocol tunneling architecture introduced in USB4 by doubling the available bandwidth while maintaining the same port / pins layout and cable structure. This has been achieved by moving the physical layer signal encoding to PAM3 (described in detail in our coverage of 80 Gbps 'Thunderbolt 5' last year). This means that existing 40Gbps USB4 cables will be able to support 80Gbps operation also.

The USB4 v2 specifications now allow tunneling of DisplayPort 2.1 signals and up to four PCIe 4.0 lanes. The data and display protocol updates also make it more efficient, with USB data tunneling capable of exceeding 20 Gbps.

One of the key updates in the move to support DisplayPort 2.1 tunneling relates to the maximum total bandwidth for four lanes in UHBR 20 transmission mode. This translates to 80 Gbps, essentially leaving nothing spare on the transmit side for any other protocol. To handle this, USB4 v2 introduces the concept of asymmetric links. In general, a USB4 link uses two bonded high-speed differential signaling pairs to transmit and receive data, allowing for 40 Gbps duplex operation (40 Gbps transmit and 40 Gbps receive) in the symmetric case. However, the lane initialization process can optionally configure the link to have 3 transmitters and one receiver on one side, and 3 receivers and one transmitter on the other. Combined with the higher data rates thanks to PAM3, this can allow the host to send out 120 Gbps, while lowering the receive bandwidth to 40 Gbps. High-resolution displays can be reliably driven without too much of a sacrifice of the bandwidth available on the transmit side for other purposes (like high-speed storage).

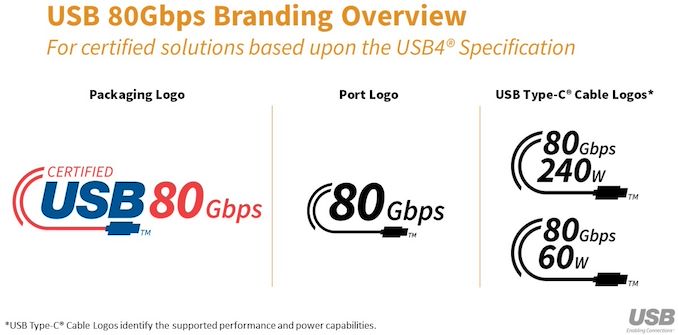

The power delivery specifications have also been updated to match the updates made in USB4 v2, and new logo guidelines have been issued for consumer-facing equipment.

Next-Generation Thunderbolt

Thunderbolt has seen incredible momentum over the last couple of years - triggered mainly by the integration of Thunderbolt controllers inside the high-volume notebook processors starting with Ice Lake. The combination of data, video, and power delivery in one port / cable makes it beneficial to a host of use-cases. In particular, the increasing popularity of hybrid work / hot-desking (monitors / networking etc. behind a dock, allowing multiple employees to just plug in their Thunderbolt-equipped systems at different times) has also served as a fillip to Thunderbolt adoption in the business / office space. Gamers and content creators have an incredible thirst for I/O bandwidth that is served well by Thunderbolt.

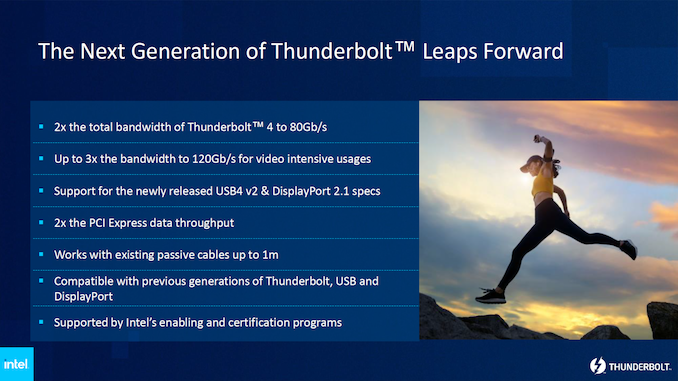

As mentioned earlier, Next Generation Thunderbolt takes the USB4 v2 specifications as baseline and makes all of the attractive optional features into mandatory ones. On top of this, Intel's integration of Thunderbolt into the notebook processors ensures that the implementation is power efficient on the host side. Making Thunderbolt mandatory for Intel Evo and vPro notebooks further cements Intel's leadership in the USB4 v2 space.

The dynamic bandwidth rebalancing feature allowing tunneling of the highest bandwidth DisplayPort 2.1 streams while still allowing usage of high-bandwidth peripherals is one of the most exciting features of USB4 v2 that is sure to be available in systems equipped with the Next Generation Thunderbolt ports.

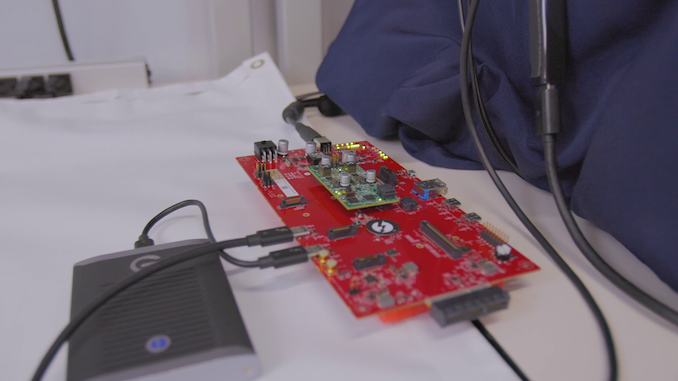

Intel's demonstration included both host and device implementations, with the host configuration shown in the beginning. A discrete GPU's DisplayPort output is fed into the host controller board, and two Type-C cables fork off, one ostensibly to the display, and another to a dock (device) with a SSD attached.

Aspects such as power delivery limits (Thunderbolt 3 / 4 support up to 15W by default) for the Next-Generation Thunderbolt ports will be clarified in the near future. Intel did not provide any information related to market availability.

Based on a glance through the USB4 v2 specifications and Intel's description of Next-Generation Thunderbolt, it is clear that Thunderbolt ports will continue to remain the Type-C port that does it all.

from AnandTech https://ift.tt/BNIe1u5

via IFTTT

0 comments:

Post a Comment